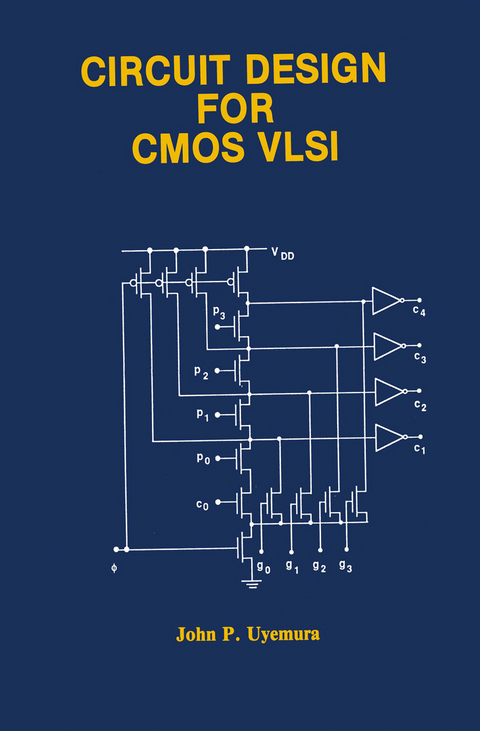

Circuit Design for CMOS VLSI

Springer-Verlag New York Inc.

9781461366096 (ISBN)

1 Introduction to CMOS.- 1.1 Why Study CMOS?.- 1.2 Basic Concepts.- 1.3 Plan of the Book.- 1.4 References.- 2 MOSFET Characteristics.- 2.1 Threshold Voltage.- 2.2 Current-Voltage Characteristics.- 2.3 p-Channel MOSFETs.- 2.4 MOSFET Capacitances.- 2.5 Junction Leakage Currents.- 2.6 Parasitic Resistances.- 2.7 Non-Rectangular MOSFET Gates.- 2.8 Mobility Variations.- 2.9 Subthreshold Current.- 2.10 Temperature Dependence.- 2.11 Scaling Theory.- 2.12 Short-Channel Effects.- 2.13 Narrow-Width Threshold Voltage.- 2.14 Hot Electrons.- 2.15 MOSFET Modelling in SPICE.- 2.16 References.- 3 The CMOS Inverter.- 3.1 Circuit Operation.- 3.2 Inverter Switching Characteristics.- 3.3 Output Capacitance.- 3.4 Secondary Parasitic Effects.- 3.5 Comparison with SPICE.- 3.6 Inverter Design.- 3.7 The Power-Delay Product.- 3.8 Temperature Dependence.- 3.9 References.- 4 Static Logic Circuits.- 4.1 General Structure.- 4.2 Series-Connected MOSFETs.- 4.3 NAND Gate.- 4.4 NOR Gate.- 4.5 Comparison of NAND and NOR Gates.- 4.6 OR and AND Gates.- 4.7 Combinational Logic.- 4.8 Exclusive-OR and Equivalence.- 4.9 Structural Variations.- 4.10 Tri-State Output.- 4.11 Pseudo-nMOS/pMOS Logic.- 4.12 Flip-Flops.- 4.13 Schmitt Trigger.- 4.14 References.- 5 CMOS Switch Logic.- 5.1 CMOS Transmission Gates.- 5.2 Transmission Gate Model.- 5.3 Layout Considerations.- 5.4 TG-Based Switch Logic Gates.- 5.5 Latches and Flip-Flops.- 5.6 Array Logic.- 5.7 Differential CVS Logic.- 5.8 Complementary Pass-Transistor Logic.- 5.9 DSL Logic.- 5.10 References.- 6 Chip Design.- 6.1 Isolation.- 6.2 CMOS Process Examples.- 6.3 Design Rules.- 6.4 Basic Layout.- 6.5 Interconnects.- 6.6 Data Transmission.- 6.7 Transmission Line Analysis.- 6.8 Crosstalk.- 6.9 Gate Arrays in CMOS.- 6.10 References.- 7 Synchronous Logic.- 7.1 Clock Signals.- 7.2 Clock Distribution and Skew.- 7.3 Clocked Static Logic.- 7.4 Charge Storage Nodes.- 7.5 Charge Leakage.- 7.6 Charge Sharing.- 7.7 Dynamic Logic.- 7.8 Domino Logic.- 7.9 Multiple-Output Domino Logic.- 7.10 Latched Domino Logic.- 7.11 NORA Logic.- 7.12 Zipper CMOS Logic.- 7.13 References.- 8 Design of Basic Circuits.- 8.1 Chip Floorplan.- 8.2 Input Protection Circuits.- 8.3 Static Gate Sizing.- 8.4 Off-Chip Driver Circuits.- 8.5 Timing and Clock Distribution.- 8.6 Memory Circuits.- 8.7 References.- 9 Analog CMOS Circuits.- 9.1 MOSFET Equations.- 9.2 Small-Signal MOSFET Model.- 9.3 Basic Amplifier.- 9.4 Voltage References.- 9.5 Current Sources.- 9.6 Differential Amplifier.- 9.7 A CMOS Operational Amplifier.- 9.8 Summary.- 9.9 References.- 10 BiCMOS Circuits.- 10.1 Bipolar Junction Transistors.- 10.2 BiCMOS Technology.- 10.3 BiCMOS Inverter.- 10.4 Comparison of CMOS and BiCMOS Performance.- 10.5 Circuit Variations.- 10.6 Logic Formation.- 10.7 Tri-state Output.- 10.8 Level Conversion.- 10.9 Summary.- 10.10 References.

| Zusatzinfo | 2 Illustrations, black and white; 480 p. 2 illus. |

|---|---|

| Verlagsort | New York, NY |

| Sprache | englisch |

| Maße | 155 x 235 mm |

| Themenwelt | Sachbuch/Ratgeber ► Natur / Technik ► Garten |

| Technik ► Elektrotechnik / Energietechnik | |

| ISBN-13 | 9781461366096 / 9781461366096 |

| Zustand | Neuware |

| Informationen gemäß Produktsicherheitsverordnung (GPSR) | |

| Haben Sie eine Frage zum Produkt? |

aus dem Bereich