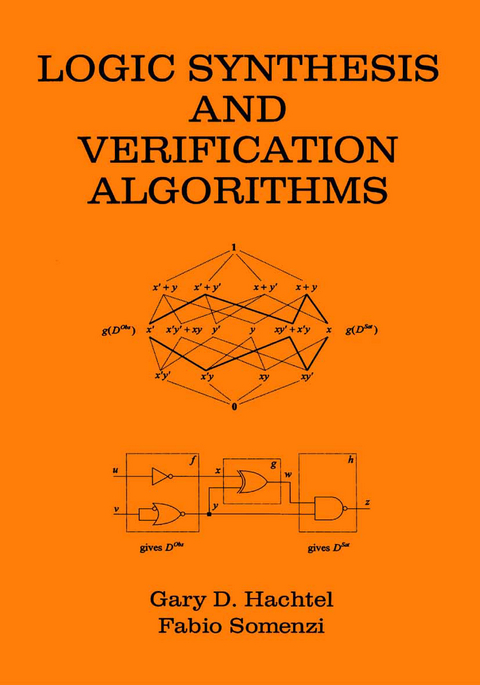

Logic Synthesis and Verification Algorithms

Seiten

2013

|

Softcover reprint of the original 1st ed. 1996

Springer-Verlag New York Inc.

978-1-4757-7036-0 (ISBN)

Springer-Verlag New York Inc.

978-1-4757-7036-0 (ISBN)

Logic Synthesis and Verification Algorithms is a textbook designed for courses on VLSI Logic Synthesis and Verification, Design Automation, CAD and advanced level discrete mathematics.

Logic Synthesis and Verification Algorithms is about the theoretical underpinnings of VLSI (Very Large Scale Integrated Circuits).

Logic Synthesis and Verification Algorithms is a textbook designed for courses on VLSI Logic Synthesis and Verification, Design Automation, CAD and advanced level discrete mathematics. It also serves as a basic reference work in design automation for both professionals and students.

Logic Synthesis and Verification Algorithms is about the theoretical underpinnings of VLSI (Very Large Scale Integrated Circuits). It combines and integrates modern developments in logic synthesis and formal verification with the more traditional matter of Switching and Finite Automata Theory. The book also provides background material on Boolean algebra and discrete mathematics.

A unique feature of this text is the large collection of solved problems.

Throughout the text the algorithms covered are the subject of one or more problems based on the use of available synthesis programs.

Logic Synthesis and Verification Algorithms is about the theoretical underpinnings of VLSI (Very Large Scale Integrated Circuits).

Logic Synthesis and Verification Algorithms is a textbook designed for courses on VLSI Logic Synthesis and Verification, Design Automation, CAD and advanced level discrete mathematics. It also serves as a basic reference work in design automation for both professionals and students.

Logic Synthesis and Verification Algorithms is about the theoretical underpinnings of VLSI (Very Large Scale Integrated Circuits). It combines and integrates modern developments in logic synthesis and formal verification with the more traditional matter of Switching and Finite Automata Theory. The book also provides background material on Boolean algebra and discrete mathematics.

A unique feature of this text is the large collection of solved problems.

Throughout the text the algorithms covered are the subject of one or more problems based on the use of available synthesis programs.

A Quick Tour of Logic Synthesis with the Help of a Simple Example.- Two Level Logic Synthesis.- Boolean Algebras.- Synthesis of Two-Level Circuits.- Heuristic Minimization of Two-level Circuits.- Binary Decision Diagrams (BDDs).- Models of Sequential Systems.- Models of Sequential Systems.- Synthesis and Verification of Finite State Machines.- Finite Automata.- Multilevel Logic Synthesis.- Multi-Level Logic Synthesis.- Multi-Level Minimization.- Automatic Test Generation for Combinational Circuits.- Technology Mapping.

| Erscheint lt. Verlag | 18.3.2013 |

|---|---|

| Zusatzinfo | XXXII, 564 p. |

| Verlagsort | New York, NY |

| Sprache | englisch |

| Maße | 178 x 254 mm |

| Themenwelt | Mathematik / Informatik ► Informatik ► Software Entwicklung |

| Mathematik / Informatik ► Informatik ► Theorie / Studium | |

| Informatik ► Weitere Themen ► CAD-Programme | |

| Mathematik / Informatik ► Mathematik | |

| Technik ► Elektrotechnik / Energietechnik | |

| ISBN-10 | 1-4757-7036-7 / 1475770367 |

| ISBN-13 | 978-1-4757-7036-0 / 9781475770360 |

| Zustand | Neuware |

| Informationen gemäß Produktsicherheitsverordnung (GPSR) | |

| Haben Sie eine Frage zum Produkt? |

Mehr entdecken

aus dem Bereich

aus dem Bereich

Band 1: Produktion

Buch | Hardcover (2024)

Springer Vieweg (Verlag)

CHF 139,95

Buch | Softcover (2023)

Beuth (Verlag)

CHF 138,60

Band 2: Automatisierung

Buch | Hardcover (2024)

Springer Vieweg (Verlag)

CHF 139,95