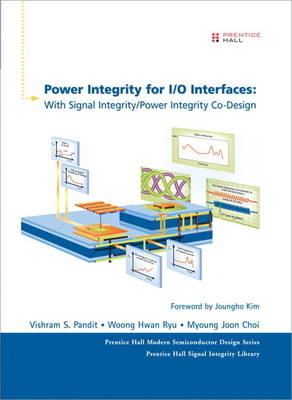

Power Integrity for I/O Interfaces

Prentice Hall (Verlag)

978-0-13-701119-3 (ISBN)

- Titel ist leider vergriffen;

keine Neuauflage - Artikel merken

The Hands-On Guide to Power Integrity in Advanced Applications, from Three Industry Experts

In this book, three industry experts introduce state-of-the-art power integrity design techniques for today’s most advanced digital systems, with real-life, system-level examples. They introduce a powerful approach to unifying power and signal integrity design that can identify signal impediments earlier, reducing cost and improving reliability.

After introducing high-speed, single-ended and differential I/O interfaces, the authors describe on-chip, package, and PCB power distribution networks (PDNs) and signal networks, carefully reviewing their interactions. Next, they walk through end-to-end PDN and signal network design in frequency domain, addressing crucial parameters such as self and transfer impedance. They thoroughly address modeling and characterization of on-chip components of PDNs and signal networks, evaluation of power-to-signal coupling coefficients, analysis of Simultaneous Switching Output (SSO) noise, and many other topics.

Coverage includes

• The exponentially growing challenge of I/O power integrity in high-speed digital systems

• PDN noise analysis and its timing impact for single-ended and differential interfaces

• Concurrent design and co-simulation techniques for evaluating all power integrity effects on signal integrity

• Time domain gauges for designing and optimizing components and systems

• Power/signal integrity interaction mechanisms, including power noise coupling onto signal trace and noise amplification through signal resonance

• Performance impact due to Inter Symbol Interference (ISI), crosstalk, and SSO noise, as well as their interactions

• Validation techniques, including low impedance VNA measurements, power noise measurements, and characterization of power-to-signal coupling effects

Power Integrity for I/O Interfaces will be an indispensable resource for everyone concerned with power integrity in cutting-edge digital designs, including system design and hardware engineers, signal and power integrity engineers, graduate students, and researchers.

Vishram S. Pandit is a technical lead in the Signal/Power Integrity Engineering team at Intel Corporation. He works on developing power delivery designs for high-speed interfaces. His focus areas include high-speed system power delivery, on-chip power delivery, and Signal/ Power Integrity co-design. Prior to Intel he worked at Hughes Network Systems on Electromagnetic Interference (EMI), Electromagnetic Compatibility (EMC), power integrity, and signal integrity technologies. He has received a B.E. (Instrumentation) from College of Engineering, Pune, India, an M.S. (Electrical Engineering) from University of Utah, USA, and an Advanced Certificate for Post-Master’s Study (Computer Science) from Johns Hopkins University, USA. He is a senior member of IEEE and a member of the CPMT Technical Committee on Electrical Design, Modeling and Simulation; and he serves as a technical program committee member for DesignCon. He was a recipient of the International Engineering Consortium’s paper awards for DesignCon 2008 and DesignCon 2009. Woong Hwan Ryu is currently a Signal/Power Integrity Engineering Manager at Intel Corporation. He has been responsible for pre-silicon signal integrity and power integrity analysis for high speed interfaces. He received his Ph.D. degree in Electrical Engineering from the Korea Advanced Institute of Science and Technology (KAIST). Dr. Ryu holds an IEEE Senior Member status; he serves as a reviewer for several IEEE journals; and he serves as a technical program committee member and organizing committee member for DesignCon. He was a recipient of the International Engineering Consortium’s paper awards for DesignCon 2006 and DesignCon 2008. Dr. Ryu has authored and co-authored more than 80 technical publications in premier journals and international conferences, and holds three issued patents and has one patent pending. Myoung Joon Choi is a technical lead in the Signal/Power Integrity Engineering team at Intel Corporation. He works on developing methodologies for high-speed interface simulation and analysis. His focus areas include high-speed system SI-PI co-simulation, on-chip signal and power integrity, and computational analysis of entire high-speed systems. Dr. Choi has received a Ph.D. and an M.S. from University of Illinois at Urbana-Champaign, Urbana, IL, USA, and a BS from Korea University, Seoul, Korea. He has authored and co-authored many technical publications in journals and conferences.

Foreword by Joungho Kim xiii

Preface xv

About the Authors xxi

Chapter 1 Introduction 1

1.1 Digital Electronic System 1

1.2 I/O Signaling Standards 2

1.2.1 Single-Ended and Differential Signaling 3

1.3 Power and Signal Distribution Network 5

1.4 Signal and Power Integrity 6

1.5 Power Noise to Signal Coupling 8

1.5.1 SSO 9

1.5.2 Chip-Level SSO Coupling 9

1.5.3 Interconnect Level SSO Coupling 10

1.6 Concurrent Design Methodology 12

References 13

Chapter 2 I/O Interfaces 15

2.1 Single-Ended Drivers and Receivers 15

2.1.1 Open Drain Drivers 16

2.1.2 Push-Pull Driver and Receiver 17

2.1.3 Termination Schemes for a Single-Ended System 18

2.1.4 Current Profiles in a Push-Pull Driver 18

Push-Pull Driver with CTT 19

Push-Pull Driver with Power Termination 22

2.1.5 Noise for Push-Pull Driver 25

2.2 Differential Drivers and Receivers 26

2.2.1 Termination Schemes for Differential System 28

2.2.2 Current Profiles in Half Differential Driver 30

2.2.3 Noise for Half Differential Driver 32

2.3 Prior Stages of I/O Interface 34

References 35

Chapter 3 Electromagnetic Effects 37

3.1 Electromagnetic Effects on Signal/Power Integrity 37

3.2 Electromagnetic Theory 39

3.2.1 Maxwell’s Equations 40

3.3 Transmission Line Theory 46

3.4 Interconnection Network Parameters: Z,Y,S and ABCD 55

3.4.1 Impedance Matrix [Z] 56

3.4.2 Admittance Matrix [Y] 57

3.4.3 The Scattering Matrix [S] 57

3.4.4 The Scattering Matrix [S] with Arbitrary Loads 59

3.4.5 Relation Between Scattering Matrix [S] and Y/Z/ABCD Matrix 61

3.5 LTI System 64

3.5.1 Reciprocal Network 64

3.5.2 Parameter Conversion Singularity 64

3.5.3 Stability 65

3.5.4 Passivity 65

3.5.5 Causality 67

References 67

Chapter 4 System Interconnects 69

4.1 PCB Technology 69

4.2 Package Types 70

4.3 Power Distribution Network 73

4.3.1 PCB PDN 73

Power Supply 74

DC/DC Converter 75

PCB Capacitors 76

PCB Power/Ground Planes 81

Impact of Vias 87

Stitching Domains Together 90

4.3.2 Package Power Distribution Network 92

4.3.3 On-Chip Power Network 93

Intentional Capacitors 94

Unintentional Capacitors 96

4.4 Signal Distribution Network 97

4.4.1 PCB/ Package Physical Signal Routing 97

Microstrip Line 97

Stripline 100

Co-Planar Waveguide 101

Coupled Lines 102

4.4.2 Package Signal Distribution Network 107

4.4.3 PCB/Package Material Properties 108

Electrical Properties of Metal 108

Electrical Properties of Dielectrics 110

Frequency-Dependent Parameters of Microstrip Line 111

4.4.4 On-Chip Signal Network 112

4.5 Interaction Between Interconnect Systems 115

4.5.1 Reference, Ground, and Return Paths 116

4.5.2 Referencing: Single-Ended and Differential Signaling 116

4.5.3 Power to Signal Coupling 118

4.6 Modeling Tools for the PDN and Signal Networks 119

References 122

Chapter 5 Frequency Domain Analysis 127

5.1 Signal Spectrum 128

5.1.1 Fourier Transform Interpretation 132

5.1.2 Important Properties of the Fourier Transform 134

Interpreting and Using Frequency Domain Representations of Waveforms 134

Key Properties of Fourier Transforms (of Interest in SI) 134

Fourier Transform Examples and Interpretation 135

Trapezoidal Pulse Fourier Transform Tool 138

5.1.3 FFT of Power Noise 141

5.1.4 Convolution and Filtering 142

5.2 Signal and Power Integrity Applications 143

5.2.1 S-Parameters with Global and Local Ground 145

5.3 Power Distribution Network Design in Frequency Domain 147

5.3.1 Impedance Response Z11 148

5.3.2 Impedance Targets for I/O Interface 150

Single-Ended Driver 151

Differential Driver 152

Prior Stages 152

5.3.3 PDN Design Example 153

Package and PCB PDN 154

PDN Co-Design: PCB, Package and Chip 155

5.3.4 On-Chip Power Delivery: Modeling and Characterization 158

Test Vehicle for On-Chip PDN 159

2D TLM Empirical On-Chip PD Modeling Method 161

On-Chip Capacitor Model Extraction 162

Modeling and Correlation for On-Chip PDN of the I/O Interface 163

EM Modeling of On-Chip PDN 165

5.3.5 Insertion Loss and Voltage Transfer Function 166

5.3.6 SSO in Frequency Domain 168

5.3.7 Power-to-Signal Coupling 170

5.4 Signal Network Design in Frequency Domain 171

5.4.1 Frequency Domain Optimization 172

5.4.2 Simulation and Correlation of Signal Network 174

5.4.3 Case Study: Crosstalk Amplification by Resonance 175

Model Correlation 177

Self-Impedance and Insertion Loss for the Entire Channel 180

Voltage Transfer Function for the Victim Bit 181

Far-End Crosstalk 182

Self-Impedance and Transfer Impedance with Different Enablers 183

5.4.4 Differential Signaling in Frequency Domain 184

References 190

Chapter 6 Time Domain Analysis 193

6.1 Time Domain Modeling and Simulation 193

6.1.1 Transient Simulations 195

6.1.2 Buffer Modeling 196

IBIS and VCR Models 196

6.2 Simulation for Optimization 198

6.2.1 Power Delivery Time Domain Specification 198

6.2.2 Controllable Design Variables for Optimization 200

Geometry and Material 201

Passive Components on PCB and Package 203

On-Chip Design Variables 203

6.3 PDN Noise Simulations 204

6.3.1 VR Tolerance and IR Drop 204

6.3.2 AC Noise Analysis 207

Supply Droop and Resonance 207

6.3.3 Internal Circuits 209

6.3.4 Final Stage Circuits 210

6.3.5 Single-Ended Systems 212

Correlation with Measurements 214

Noise Measurements at the Receiver 215

6.3.6 Differential Systems 217

6.3.7 Logic Stage 220

6.4 Jitter Impact for Time Domain Analysis 221

6.4.1 Jitter Impact Due to PDN Noise 222

6.4.2 Jitter Due to the SSO 223

Single-Ended System 223

Differential System 228

References 231

Chapter 7 Signal/Power Integrity Interactions 233

7.1 Background 234

7.2 Root Cause Analysis 236

7.3 SSO Coupling Mechanism 238

7.4 Case Study I: DDR2 800 Control Signal 241

7.4.1 Noise Source 243

7.4.2 Coupling Mechanism 244

7.4.3 Resonant Structure on Control Networks 245

7.4.4 Proposed Solutions 247

7.5 Case Study II: DDR2 667 Vref Bus 248

7.5.1 Noise Source 249

7.5.2 Coupling Mechanism 249

7.5.3 Resonance Structure 250

7.5.4 Proposed Solutions 252

7.6 Referencing/Stitching/Decoupling Effects--Single-Ended Interface 258

7.7 Stitching Effects--Differential Interface 263

7.7.1 VNA Measurement Results 271

7.7.2 Modeling and Measurement Correlations 273

7.7.3 System-Level Impact Evaluation 274

7.8 EMI Trade-Off 276

7.8.1 Power Islands Radiation 276

References 282

Chapter 8 Signal/Power Integrity Co-Analysis 285

8.1 Identifying Controllable Parameters 286

8.2 SI-PI Modeling and Simulation 288

8.2.1 Modeling SI-PI Compatible Buffers 288

8.2.2 Modeling On-Chip Passive Components 290

8.2.3 Modeling Off-Chip Passive Components 291

8.2.4 Model Check and Integration 291

8.2.5 Construction of SI-PI Co-Simulation 292

8.2.6 PDN Resonance Excitation of Driver Bit Pattern 292

8.2.7 Worst-Case Eye 294

8.2.8 Running SI-PI Co-Simulation 296

ISI and Minimal ISI 297

ISI and SSO 298

ISI and Crosstalk 299

ISI, SSO, and Crosstalk 299

8.3 SI-PI Co-Analysis 301

8.3.1 Time Domain Analysis 301

Optimization Using Sweep Parameters and Noise Decomposition 302

Simple Comparison of Eye 305

8.3.2 Eye Diagram Analysis 308

8.3.3 Linear Interaction Indicator 309

Single-Ended Signaling SI-PI Performance and Linearity 315

Differential Signaling SI-PI Performance and Linearity 317

SI-PI Linear Interaction Indicator 319

8.4 SI-PI Co-Simulation and Co-Analysis Flow: Summary 321

References 322

Chapter 9 Measurement Techniques 325

9.1 Frequency Domain Characterization 325

9.1.1 Vector Network Analyzer (VNA) 326

9.1.2 Smith Chart 327

9.1.3 Low-Impedance VNA Measurement for Power Delivery Network 329

9.1.4 On-Chip Characterization 335

On-Chip Interconnect 2D Modeling and Correlation 338

On-Chip Interconnection Line Performance Versus Different Structures 345

On-Chip PDN Characterization 349

9.1.5 Pad Capacitance Characterization 350

Lower- and Upper-Frequency Limit 350

De-Embedding Method 351

9.1.6 Power Delivery-to-Signal Coupling Measurement 353

9.2 Equivalent Circuit Model Extraction 355

9.2.1 Need for an Equivalent Circuit Model 355

Validation Purpose 355

Simulation Purpose 356

9.2.2 Extraction Methodology 357

Numerical Error 358

9.2.3 Extraction Examples 358

Receiver Model for SI 358

PDN Model 360

Topology Identification 360

9.2.4 Extension to Multiport Measurement 361

9.3 Time Domain Characterization 361

9.3.1 Time Domain Reflectometry (TDR) 361

Development of 9ps TDR Measurement Setup 363

Package Validation Using TDR 365

Differential TDR and TDT 371

9.3.2 PDN Noise Measurement 372

9.3.3 SSO Coupling Measurement in Time Domain 376

9.3.4 Jitter Measurement 379

References 380

Index 383

| Erscheint lt. Verlag | 21.10.2010 |

|---|---|

| Verlagsort | Upper Saddle River |

| Sprache | englisch |

| Maße | 183 x 241 mm |

| Gewicht | 780 g |

| Themenwelt | Mathematik / Informatik ► Informatik |

| Technik ► Elektrotechnik / Energietechnik | |

| ISBN-10 | 0-13-701119-9 / 0137011199 |

| ISBN-13 | 978-0-13-701119-3 / 9780137011193 |

| Zustand | Neuware |

| Haben Sie eine Frage zum Produkt? |

aus dem Bereich