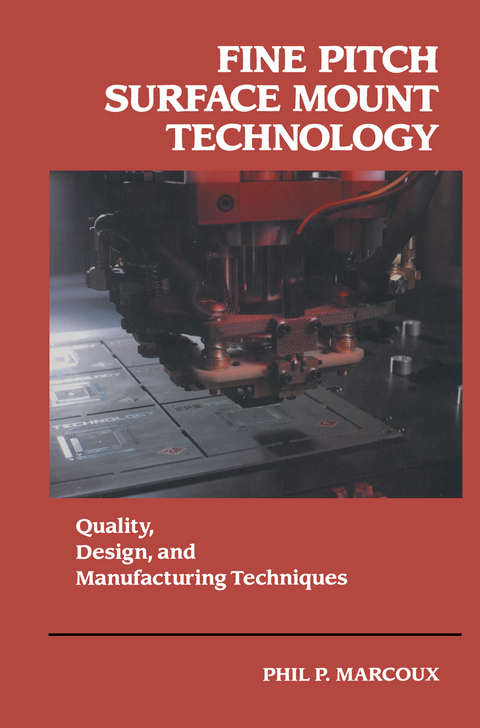

Fine Pitch Surface Mount Technology

Van Nostrand Reinhold Inc.,U.S. (Verlag)

978-0-442-00862-8 (ISBN)

1 Introduction to Fine Pitch Technology (FPT).- 1.0 Introduction.- 1.1 What is Fpt?.- 1.2 The Benefits of Fine Pitch Technology.- 1.3 The Motivation for Fine Pitch Technology.- 1.4 Comparison of Fpt with Through-Hole and Surfacemount Technologies.- 1.5 Fine Pitch Technology Obstacles and Issues.- 2 The Family of FPT Packages.- 2.0 The Evolution of Fpt Packages.- 2.1 Introduction and Construction of Fine Pitch Packages.- 2.2 Quad Flat Packages.- 2.3 Plastic Quad Flat Packages.- 2.4 Small Outline Packages.- 2.5 Tape Automated Bonded and Guard Ring Packages.- 2.6 Package Handling and Shipping.- 2.7 Package Reliability and Quality.- 2.8 Issues When Selecting an Fpt Package.- 3 Fine Pitch Product Applications.- 3.0 Applications.- 3.1 Product Applications.- 3.2 Package Usage.- 4 Printed Circuit Boards for Fine Pitch Technology.- 4.0 Basic Pcb Processing.- 4.1 Material Options and Properties.- 4.2 Fabrication and Assembly Issues.- 4.3 Composite Electrical Properties.- 4.4 Composite Thermal Properties.- 5 Solder and Application Methods.- 5.0 Solder.- 5.1 Solder Alloy Choices.- 5.2 Flux.- 5.3 Solvents and Thixotropes.- 5.4 Specifying a Paste.- 5.5 Storage.- 5.6 Paste Quality Control and Testing.- 5.7 Applying Solder Paste.- 6 Package Placement.- 6.0 Placement.- 6.1 Placement Options.- 6.2 Additional Placement System Features.- 6.3 Throughput Requirements.- 7 Solder Reflow.- 7.0 Reflow Defined.- 7.1 The Dynamics of the Reflow Process.- 7.2 The Heat Source.- 7.3 Selecting a Reflow Method.- 7.4 Changing Component Location During Reflow.- 8 Post Reflow Cleaning.- 8.1 Successful No-Clean.- 9 Inspection, Rework, and Repair.- 9.0 Inspection.- 9.1 Rework and Repair.- 10 Design for Reliability Guidelines.- 10.1 Defining Solder Joint Reliability.- 10.3 Cause of Solder Joint Fatigue.- 10.4Solder Joint Prediction Models.- 10.5 Electronic Product Use Conditions.- 10.6 General Design for Reliability Guidelines.- 11 Design for Testability.- 11.0 Basics of Electrical Testing Pcas.- 11.1 Contacting the Assembly.- 11.2 Disadvantages of In-Circuit Testing.- 11.3 Alternatives to In-Circuit Testing.- 11.4 Successfully Using Ict For Fpt Testing.- 12 Design for Manufacturability.- 12.0 General Dfm Guidelines.- 12.1 The Rules of Dfm.- 12.2 Implementing Dfm.- 12.3 Dfm Summary.- 13 Specific Design Guidelines for FPT Packages.- 13.1 Package Selection.- 13.2 Package Placement on the Board.- 13.3 Land Pattern Size.- 13.4 Trace Routing and Protection.- 13.5 Thermal Management.- 13.6 Fabrication of the Board.- 13.7 Stencil Fabrication.- Appendix A Addresses of Standards Organizations.- Appendix B Summary of SMT Semiconductor Outlines from JEDEC Publication 95.- Appendix C Summary of Important Component, Material,Process and Design Standards.

| Zusatzinfo | 173 Illustrations, black and white; XI, 340 p. 173 illus. |

|---|---|

| Verlagsort | New York |

| Sprache | englisch |

| Maße | 155 x 235 mm |

| Themenwelt | Mathematik / Informatik ► Informatik |

| Technik ► Elektrotechnik / Energietechnik | |

| ISBN-10 | 0-442-00862-7 / 0442008627 |

| ISBN-13 | 978-0-442-00862-8 / 9780442008628 |

| Zustand | Neuware |

| Haben Sie eine Frage zum Produkt? |

aus dem Bereich